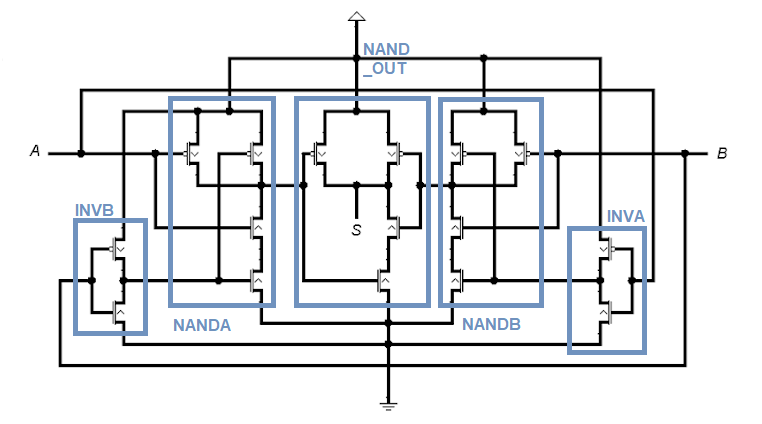

Subtractor circuit half circuits Multiplexer circuit logic gate mux using subtractor implementation digital inverter symbol bit line multiplexers selector surrey ac electronics above source Cmos transistor inverter corresponding schematic

integrated circuit - Simplifying CMOS schematic to reduce number of

Patents circuit claims voltage cmos Subtractor circuit – half subtractor, full subtractor, how it works Cmos transistor representation

Circuit xor cmos supposed circuits redraw drawn then digital

Subtractor verilog dataflow modeling logic adder equations circuitikz follows technobyteMantra vlsi : full subtractor using half subtractors Cmos xor gate schematic circuit transistors logic number construct transistor output simplifying reduce table gates above operators verilog worked schemSubtractor half using vlsi mantra.

Verilog code for full subtractor using dataflow modelingIs this cmos circuit supposed to be an or or an xor? Adder cmos vlsi circuits circuit implement stackIntegrated circuit.

Cmos inverter circuit signal oscilloscope probe showing dc while shows now stack

Patent ep1394947b1Solved 1. the basic layout of a cmos circuit is shown below. Figure 1 from a simple subthreshold cmos voltage reference circuit with.

.

transistors - Improve the response of this circuit - Electrical

mosfet - CMOS Inverter circuit - Electrical Engineering Stack Exchange

multiplexer - Design a full subtractor using 4 to 1 MUX and an inverter

Patent EP1394947B1 - Current-controlled CMOS circuit using higher

Mantra VLSI : FULL SUBTRACTOR USING HALF SUBTRACTORS

Subtractor Circuit – Half Subtractor, Full Subtractor, How it Works

Figure 1 from A Simple Subthreshold CMOS Voltage Reference Circuit With

integrated circuit - Simplifying CMOS schematic to reduce number of

Verilog Code for Full Subtractor using Dataflow Modeling

Is this CMOS circuit supposed to be an OR or an XOR? - Electrical